Yes, clocking and jitter really matter because they directly impact your system’s reliability and performance. Precise clock signals make certain your data stays synchronized, while excessive jitter can cause errors, data loss, or system crashes. Even tiny timing variations disrupt high-speed operations. If you want to understand how to keep your system stable and avoid these issues, exploring these concepts further will give you valuable insights.

Key Takeaways

- Clocks generate precise timing signals essential for synchronization in digital systems.

- Phase noise causes jitter, disrupting timing stability and increasing error rates.

- Excessive jitter can lead to data loss, system crashes, and unreliable operation.

- Maintaining low phase noise and timing stability is critical for high-speed, accurate systems.

- Engineers use filtering and PLLs to minimize jitter and ensure reliable system performance.

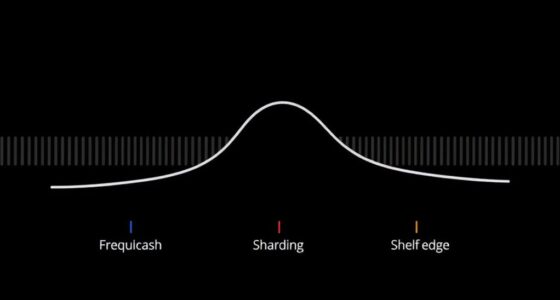

Have you ever wondered how digital systems stay synchronized? It’s a fascinating process that relies heavily on precise timing signals generated by clocks. These clocks act as the heartbeat of electronic devices, coordinating data transfer and making sure everything runs smoothly. But maintaining perfect synchronization isn’t simple, and factors like phase noise can threaten timing stability. Phase noise refers to the small, rapid fluctuations in a signal’s phase, which can cause jitter and disrupt the clean, steady timing needed for high-performance systems. When phase noise increases, it becomes more challenging for the system to distinguish between valid signals and noise, leading to potential errors and degraded performance.

Timing stability is essential because it determines how reliably a system can keep its timing signals consistent over time. Even tiny deviations can cascade into significant problems, especially in applications like telecommunications, data centers, or high-speed computing. If your clock signal isn’t stable, data may arrive early or late, causing synchronization issues that can corrupt information or slow down processes. That’s why engineers pay close attention to how well a clock maintains timing stability, often designing circuits to minimize phase noise and guarantee a steady, predictable output. They use specialized oscillators and phase-locked loops (PLLs) to lock onto a reference frequency, reducing the impact of phase noise and keeping the system synchronized.

Understanding the importance of phase noise and timing stability helps you appreciate why jitter matters so much in digital systems. Jitter refers to the small timing variations in a clock signal, which can be caused by phase noise or other disturbances. Excessive jitter can lead to bit errors, data loss, or system crashes. As technology advances, the demand for cleaner, more stable clocks increases, especially in applications requiring high data rates and low latency. That’s why manufacturers invest heavily in high-quality oscillators and filtering techniques to minimize phase noise and maximize timing stability. They aim to produce signals that stay as consistent as possible, even in noisy environments. Real-time analytics can help monitor and optimize these parameters for better performance.

Ultimately, whether you’re designing a new system or troubleshooting an existing one, recognizing the influence of phase noise and timing stability is key. By controlling these factors, you guarantee your digital systems perform accurately and reliably. Jitter might seem like a small detail, but it’s often the difference between seamless operation and frustrating errors. So, yes, in the world of digital electronics, clocking and jitter absolutely matter—they’re fundamental to keeping everything synchronized, precise, and efficient.

Frequently Asked Questions

How Does Temperature Affect Clock Stability?

Temperature affects clock stability by causing thermal expansion, which alters the physical properties of the oscillator’s components. As temperature changes, you’ll notice frequency drift, making your clock less accurate. Higher temperatures can increase oscillator frequency, while lower temperatures decrease it. To maintain stability, you should use temperature-compensated or oven-controlled oscillators, which help minimize thermal effects and keep your clock running precisely despite temperature fluctuations.

Can Jitter Be Completely Eliminated in Digital Circuits?

You can’t completely eliminate jitter, because “nothing is perfect.” While advanced clock calibration and jitter mitigation techniques substantially reduce it, some residual jitter always remains due to factors like power supply noise and device imperfections. You endeavor to minimize jitter to improve circuit performance, but accepting a small amount is realistic. Continuous improvements in design and technology help manage jitter effectively, even if total elimination remains impossible.

What Are the Best Practices for Clock Distribution?

You should guarantee proper clock distribution by minimizing clock skew through balanced routing and matched load capacitances, which keeps timing consistent across your circuit. Use low-impedance clock buffers and controlled impedance traces to reduce jitter. Additionally, stabilize your power supply to prevent fluctuations that can cause timing errors. Proper grounding and decoupling are essential, as they help maintain signal integrity and improve overall clock distribution performance.

How Do Phase-Locked Loops (PLLS) Influence Jitter?

You should know that phase-locked loops (PLLs) influence jitter by controlling phase noise and loop bandwidth. When the loop bandwidth is narrow, it filters out high-frequency phase noise, reducing jitter, but may slow lock time. Conversely, a wider bandwidth allows faster locking but can let more phase noise through, increasing jitter. Properly tuning these parameters guarantees your system maintains signal integrity with minimal jitter.

Are There Industry Standards for Acceptable Jitter Levels?

Think of jitter measurement as a tightrope walk—balance is everything. Industry standardization sets the safety net, defining acceptable jitter levels to keep your systems steady. While standards vary across applications, most follow guidelines like those from IEEE or JEDEC, ensuring your equipment performs reliably. Staying within these limits means your signals remain synchronized, preventing errors and ensuring smooth operation in your high-tech world.

Conclusion

So, while clocking and jitter might seem like minor ripples on your circuit’s surface, they subtly influence your system’s harmony. Think of them as gentle waves guiding a boat—if they’re too rough, your voyage becomes bumpy. By paying attention to these nuances, you ensure your signals flow smoothly, like a calm stream. Ultimately, mastering clocking and jitter helps keep your digital symphony playing in perfect tune, quietly but powerfully enhancing your design’s rhythm.